Tim Wescott

www.wescottdesign.com

A Thesis Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering by

August 17, 1990

**APPROVED:**

Dr. Per K. Enge, Major Advisor

Dr. John A. Orr, Head of Department

The Global Positioning System (GPS) is now in operation, and many improvements to its performance are being sought. One such improvement is Differential GPS (DGPS), where known errors in the GPS broadcast are identified and the corrections broadcast to the end user [12]. One implementation of DGPS being considered is the use of coastal marine radio direction finding (RDF) radiobeacons in the 285-325kHz band as transmitters for the DGPS broadcast. The normal RDF beacon signal consists of a continuous carrier on a one kilohertz boundary plus a Morse-code identification signal 1025Hz above the carrier. In the DGPS/radiobeacon implementation proposed for the US coastal regions, the the differential data link signal uses minimum shift keying (MSK) at a data rate of 25, 60,100, 200, or 400 baud (the exact baud rate has not yet been decided). This MSK signal is centered between the RDF beacon carrier and identification signal.

At the frequencies that these radiobeacons are operated, the prevailing atmospheric noise is both non-Gaussian and very strong. This noise characteristic makes the design of a long-range data link difficult. One solution that has been proposed is the use of forward error correction (FEC) coding of the data. The performance of FEC decoders can be improved by the use of a soft decision receiver, which delivers both bit decisions and information about the validity of the bit decisions [15]. This work describes the design of a radio receiver for DGPS/radiobeacon service which is capable of reception of 400 baud MSK in the DGPS/radiobeacon band. The receiver is designed to be easily augmented to provide soft decisions and easily modified to receive MSK at data rates of 25 to 400 baud. The radio is a microprocessor controlled dual conversion superheterodyne with an audio frequency of 1kHz. The demodulator runs on the same microcomputer that controls the radio. The weak-signal performance of the demodulator is very good: the vs. bit error rate performance of the demodulator is only a couple of dB worse than the theoretical performance of differential phase-shift keying. The radio has a noise floor of -114dBm referenced to its 500Hz wide audio bandwidth and a 3rd order inter modulation intercept of +7dBm for a dynamic range of 83dB,

This work concludes with a thumbnail analysis of the operations needed to implement a soft bit decision estimator, and some suggestions for the implementation of said soil bit decision estimator.

www.wescottdesign.com

#### The Story of the Web Edition

This Master's Thesis is a companion to a radio receiver that I built for Per Enge, then of Worcester Polytechnic Institute in Worcester, Massachusetts, in 1989 and 1990. The motivation for the receiver on Per's part was to get his hands on something that would receive the then-experimental US Coast Guard differential GPS data link broadcasts. Per needed a radio receiver that would not only receive MSK at the correct frequency, but would make "soft" decisions, so that he and his team of graduate students could experiment with advanced forward-error-correction decoding schemes. I needed a thesis topic.

My search for a thesis advisor was a well-thought out, highly detailed study. Basically, I took a list of all the electrical engineering faculty at WPI that had anything remotely to do with communications equipment, and I went knocking on doors. Fortunately for both Per and I, his was the first office on my list that was occupied. I explained that I was looking for a thesis topic that would involve communications equipment, preferably radio. He pulled out a schematic of a radio receiver and said "can you build something like this?"

I had reservations about the radio he wanted me to build. As I found out much later, he had reservations about my ability to build a radio. But the project worked out well for both of us – I got to build a radio receiver for my Master's Thesis and I got some excellent training in writing book-length documents. Per got what turned out to be only the second receiver designed for USCG DGPS radio beacon service. The receiver served him well for several years, and in the end I was fortunate enough to get it back to add to my collection.

When I wrote down this Master's Thesis, I thought I was doing it to check off a box in my graduation requirements, to learn a bit about writing really long (and even slightly scholarly) documents, and to make my Thesis advisor happy. I kept a copy of it on my bookshelf mostly out of pride, although I did have occasion to refer to one or two tidbits contained within. I assumed that I had wrung all of the use out of it that it was ever going to get.

Then, 15 years after it was written, I started coming across queries on USENET asking how to design and construct MSK receivers. People wanted to build MSK receivers, but were unable to find information on how to do the job. After some fruitless web searches, I decided that since I'd already done it once I should write a comprehensive article on the design and construction of an MSK receiver. After re-reading my Master's thesis, I decided that I already had, and all I needed to do was to post it to the web.

I solicited help on USENET, and Joel Kolstad, KE7CDV, kindly stepped forward and scanned my entire thesis into electronic form. Since that time, this thesis has been popular enough reading that we have run the whole thing through OCR software, turning it into text, and have made it into a document that is (hopefully) more readable than the original scanned-in version.

Keep in mind as you read this that the methods presented in this document are just one way to implement an MSK receiver. I designed this receiver and it worked, but I would never, ever suggest that it is the optimal design – in fact, many of the central design decisions of this radio

were made late at night under intense schedule pressure by a neophyte engineer. So read it for the basic theory and as an example of how *one* such radio was built, but don't assume that it can't be vastly improved upon.

# **Table of Contents**

| 1 | Introduction                                                   | 6  |

|---|----------------------------------------------------------------|----|

|   | 1.1 The Global Positioning System                              | 6  |

|   | 1.2 DGFS and Radiobeacons.                                     | 7  |

|   | 1.3 Minimum Shift Keying                                       | 8  |

|   | 1.4 Atmospheric Noise and Forward Error Correction             | 8  |

|   | 1.5 Side Information                                           | 8  |

|   | 1.6 Outline of Thesis                                          | 8  |

| 2 | The Radio                                                      | 10 |

|   | 2.1 The Mixing Scheme                                          | 10 |

|   | 2.2 The Local Oscillator                                       | 12 |

|   | 2.3 Front end Circuitry                                        | 14 |

|   | 2.3.1 Antenna Coupler                                          | 14 |

|   | 2.3.2 RF filter, Mixer                                         | 15 |

|   | 2.3.3 IF preamp                                                | 15 |

|   | 2.4 IF Filter                                                  | 16 |

|   | 2.5 IF Amplifier                                               | 16 |

|   | 2.6 2nd Mixer and 2nd Local Oscillator                         | 17 |

|   | 2.7 Audio Amplifier and AGC Amplifier                          | 17 |

|   | 2.8 Microprocessor                                             | 17 |

|   | 2.8.1 The MC68HC11                                             | 17 |

| 3 | The Demodulators                                               | 19 |

|   | 1.7 MSK                                                        | 20 |

|   | 3.1.1 MSK Detection                                            | 23 |

|   | 3.1.2 Synchronization                                          | 24 |

|   | 3.2 Microprocessor based demodulator                           | 25 |

|   | 3.3 The Timing Recovery Algorithm                              | 26 |

|   | 3.3.1 Phase error estimation                                   |    |

|   | 3.3.2 The gain blocks                                          |    |

|   | 3.3.3 Loop Filter Calculations and Bandwidth                   | 32 |

|   | 3.3.4 Limit Cycles                                             | 33 |

|   | 3.3.5 Lock Acquisition                                         |    |

|   | 3.3.6 Carrier Stability and Carrier l\Loop Bandwidth           | 34 |

|   | 3.4 The Correlation Detector                                   | 36 |

| 4 | Tests of Radio Performance                                     |    |

|   | 4.1 Bit error rate in the presence of Gaussian noise           | 39 |

|   | 4.2 BER in the presence of an interfering carrier              |    |

|   | 4.3 3rd Order Inter modulation Performance                     |    |

|   | 4.4 Receiver Noise Floor                                       |    |

| 5 | Summary, Some Comments on Soft Bit Decisions, and Further Work | 49 |

|   | 5.1 Summary                                                    | 49 |

|   | 5.2 Some Comments on Soft Bit Decisions                        | 49 |

|   | 5.2.1 The Auxiliary Channel Method                             | 49 |

www.wescottdesign.com

| A DGPS/Radiobeacon Receiver for Minimum Shift Keying with Soft Decision Capabilities |     |

|--------------------------------------------------------------------------------------|-----|

| 5.2.2 The In-Channel Method                                                          | 49  |

| 5.3 Suggestions for Further Work                                                     | 52  |

| 1 Appendix A                                                                         | 54  |

| 1.1 The Continuous-time MSK Demodulator                                              | 54  |

| 2 Appendix B                                                                         | 57  |

| 2.1 Receiver Software                                                                | 57  |

| 3 Appendix C                                                                         | 87  |

| 3.1 Transmitter Software                                                             |     |

| 4 Appendix D                                                                         |     |

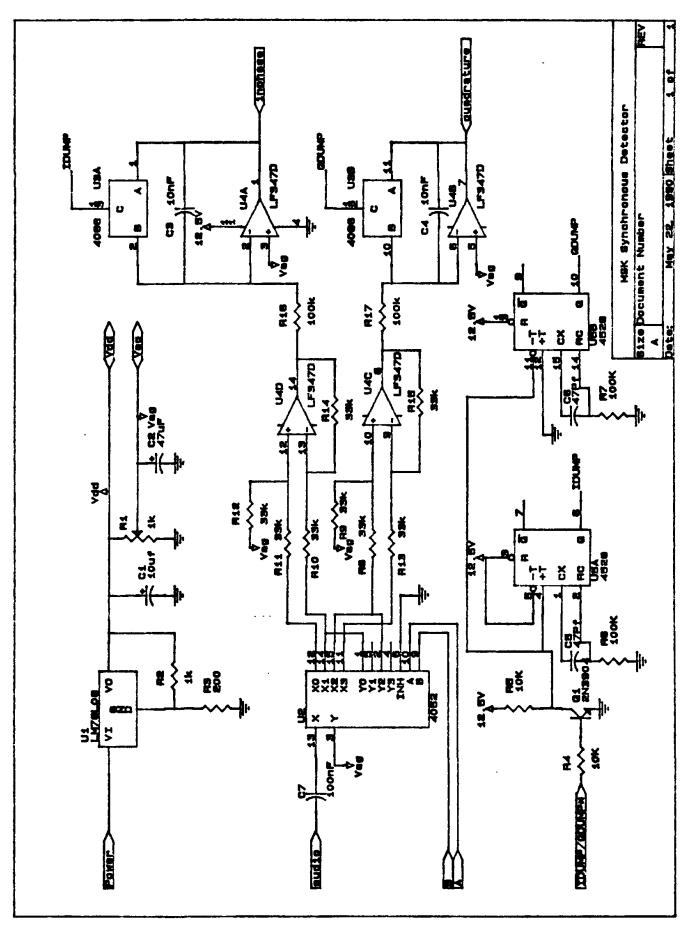

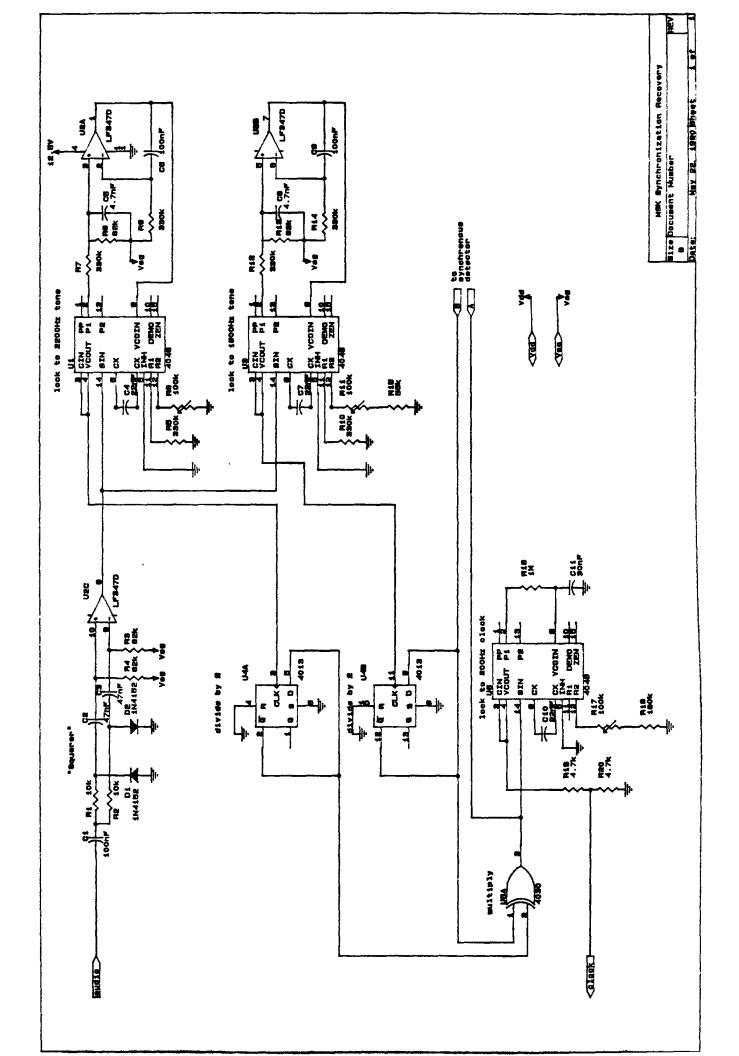

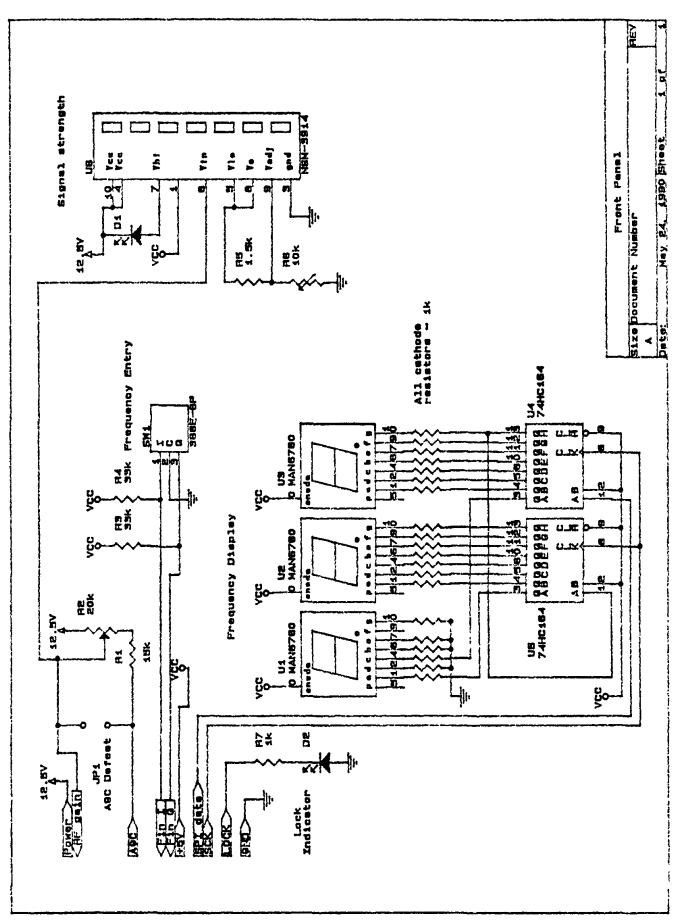

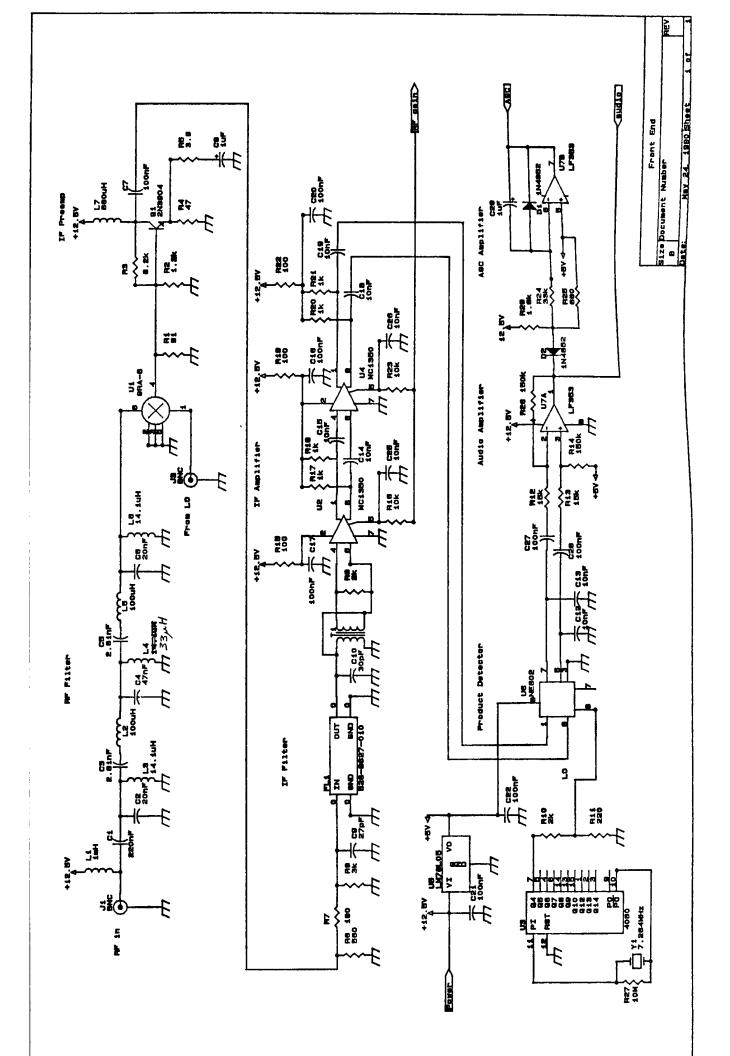

| 4.1 Schematics                                                                       |     |

| 5 Bibliography                                                                       | 111 |

# 1 Introduction

### 1.1 The Global Positioning System

The Global Positioning System (GPS) is a worldwide real-time navigation system, currently being developed by the Department of Defense, that will broadcast ranging signals from a constellation of 24 satellites. Various mechanisms limit the accuracy of users' range measurements and ultimately their position determinations. These mechanisms include some errors that vary rapidly in time and space, and others that vary slowly. The slowly varying errors include unmodeled ionospheric delay and "selective availability", which is intentionally introduced for purposes of national defense. Slowly varying errors can be corrected using differential techniques, providing a channel is available to convey the differential correction information to users.

Differential GPS (DGPS) requires a local reference station, a communication link to users, and user GPS receivers [12]. The reference station has its own high quality GPS receiver that continuously measures range to all satellites in view, and determines local range errors using its known surveyed location. Corrections for the local errors arc then communicated to users, who remove the errors from the ranging information determined by their own GPS receiver. Civilian users can improve their position fixing accuracy from 100 meters to better than 30 meters using differential corrections, making DGPS potentially suitable for many precision civilian navigation applications.

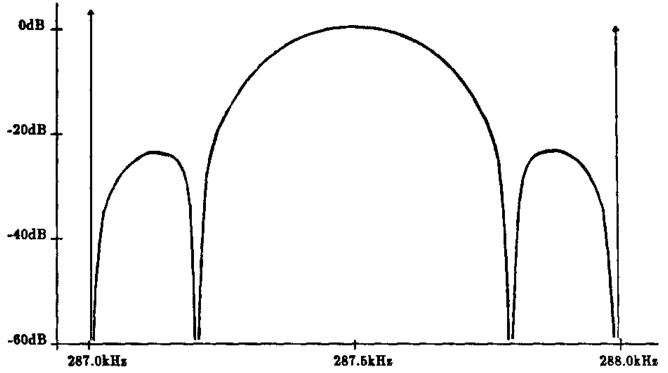

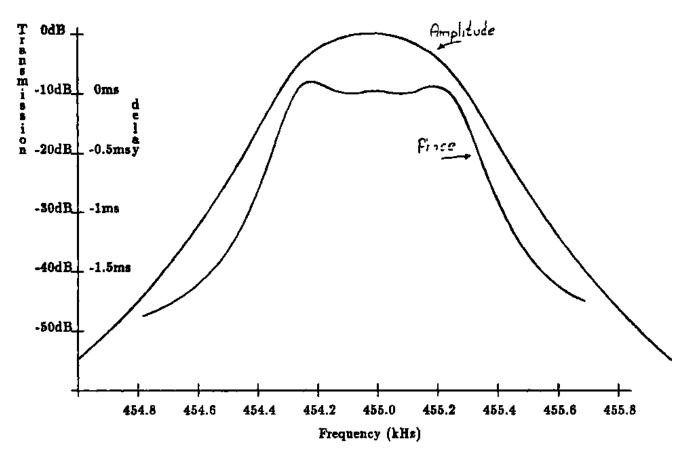

*Figure 1: Example spectrum of a DGPS/Radiobeacon operating at 287kHz with a 400 baud minimum shift keying signal between the radiobeacon carrier and ID signals*

The US Coast Guard maintains and operates a system of marine radiobeacons, located along the Atlantic, Gulf and Pacific coasts and on the Great Lakes [4]. These radiobeacons provide a 2-line fix capability out to 50 nautical miles or the 100 fathom curve, whichever is greater. They operate in the 285-325 kHz band, with a nominal channel spacing of 1kHz. Similar radiobeacons are operated by various European countries at a channel spacing of 1kHz, which is currently being reduced to 500Hz [6].

These radiobeacons offer an attractive communications link for DGPS because they are widespread, located near major harbors, and, being MF, would require inexpensive user receivers. At this writing, it appears that the messages will be transmitted using minimum shift keying (MSK) using baud rates from 25 to 400, and perhaps using forward error correcting (FEC) with the MSK carrier 500Hz above the radiobeacon carrier with a 3dB subcarrier protection ratio (for the US Coast Guard version) [6]. Figure 1 shows an example of the spectrum of a radiobeacon with a 400 baud DGPS MSK data link. Previous investigators have found that a 100 baud DGPS signal can be transmitted on a radiobeacon link with minimal interference to radio direction finding sets [6].

#### 1.3 Minimum Shift Keying

The most likely candidate for the transmission format for the DGPS data link is minimum shift keying

(MSK). MSK can be thought of either as phase coherent frequency shift keying (FSK) with a deviation ratio of 1/2 (ie. the difference between the mark and space frequencies is 1/2 the baud rate), or as sinusoidally weighted offset quadrature phase shift keying (OQPSK). A thorough analysis of MSK is given in [1] and [2], and a review is given at the beginning of chapter 3. MSK can be generated as phase coherent FSK, and optimally demodulated in Gaussian noise as PSK [1, 2].

MSK has a number of advantages for a DGPS data link. It is spectrally compact [2], which is an advantage in the bandwidth-limited LF range. Because it is a type of FSK it has a constant envelope, which makes it easier to transmit. It lacks sudden phase changes, so it is only minimally distorted when being radiated by a highly reactive antenna (which is important at LF, where the antenna is usually only .05 wavelength long).

## 1.4 Atmospheric Noise and Forward Error Correction

At 300 kHz, the most important limit to DGPS/Radiobeacon range is atmospheric noise, largely due to lightning. This noise is bursty and highly non-Gaussian. Specifically, the probability density of this noise is much greater in the high-power 'tails' than is the case with Gaussian noise [10].

In the case of Gaussian noise, the bit error rate (BER) can be reduced by increasing the bit interval (ie., decreasing the baud rate) or by increasing the transmitted power. This is also true for typical atmospheric noise, but the improvement in the BER for a given increase in power or bit interval is not nearly as great as for Gaussian noise.

Another way to reduce the ultimate BER is to use forward error correction (FEC) [15]. Using a rate 1/4 FEC code at 400 baud the performance of a DGPS/Radiobeacon link is slightly better than using no FEC and a 50 baud link [11].

## 1.5 Side Information

FEC algorithms can yield higher performance if they are given additional information about the validity of the data that they are decoding, ie., if the demodulator determines that a bit decision is questionable, that bit is flagged for the FEC decoding algorithm [15]. I have built a radio and demodulator which collect enough information to make decisions about this side information. The design of the radio will be presented in this report.

## 1.6 Outline of Thesis

This thesis is organized onto three major chapters, two minor chapters, and some appendices.

Minor chapters. Chapter one introduces this thesis. Chapter five gives numerous suggestions for further work on the subject of extracting side information and concludes the thesis

Major chapters. Chapter two is a description of the radio from the antenna to the input of the MSK demodulator. Chapter three is a discussion of MSK, MSK demodulators is general, and a description of the final MSK demodulator design settled on. Chapter four describes, and presents the results of, several performance tests for the radio and demodulator.

Appendices. Appendix A is a description of an analog implementation of MSK demodulation which

does not work well in environments where the noise level is high enough to require FEC, but works very well at lower noise levels. Appendix B is a listing of the receiver software in Motorola 68HC11 assembly code.

# 2 The Radio

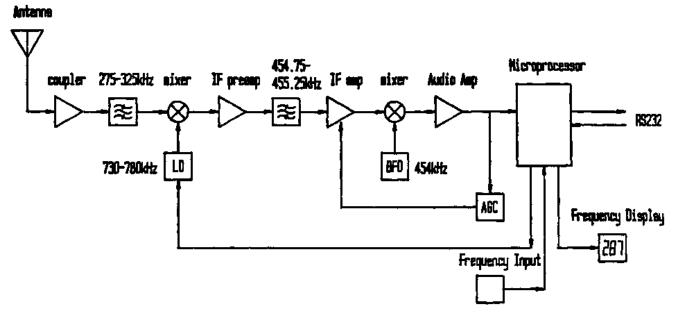

The basic radio design ahead of the demodulator is a fairly standard double conversion superheterodyne receiver. Figure 3 is a block diagram of the receiver. The antenna is connected to a coupler, which acts as a preamp and an impedance converter, allowing the use of a one-meter whip antenna. The signal from the coupler is fed into the RF filter, which is a five pole Chebychev bandpass filter, designed to pan frequencies in the 275-325 kHz range. The filtered signal is then mixed up to 455 kHz and amplified. This IF signal is filtered by a Collins mechanical filter, which is roughly Gaussian with a 500 Hz bandwidth.

I will start the description of this radio by describing the mixing scheme. Then I will describe the local oscillator (LO). Finally, I will describe the all of the modules along the main signal path: the radio frequency (RF) filter and the mixer, the intermediate (IF) preamp, the IF filter, the IF amplifier, the second mixer and second LO, the audio amplifier and AGC amplifier, and the microprocessor.

### 2.1 The Mixing Scheme

The mixing scheme is based on the following criteria: ready availability of IF components, ease of design of the RF bandpass filter, ease of design of the local oscillator, and relative freedom from harmonic mixing.

455kHz is a very common IF frequency, and it is easy to obtain IF filters which operate at this frequency. As discussed below, an IF frequency of 455kHz also satisfies the other criteria.

The local oscillator (LO) frequency was chosen to be above the IF and RF frequencies. This causes the LO frequency to be the sum of the desired receive frequency and the IF frequency

( $f_{lo}=f_{rf}+f_{if}$ ). The LO range is 730-780kHz.

Figure 2: WPI DGPS/Radiobeacon Receiver Block Diagram

Placing the LO above the RF and IF has several advantages. First, the frequency difference between the desired receive band and the band of possible image frequencies is maximized, simplifying the design of the bandpass filter. An image frequency is an undesired RF frequency that can mix to the IF frequency and be received. For example, if the desired receive frequency is 287.5kHz, the LO frequency is

$f_{lo}$ =455kHz+287.5kHz=742.5kHz

. If there is a signal at the mixer with a frequency of 1197.5kHz, it will be received as well

1197.5 kHz - 742.5 kHz = 455 kHz. Second, placing the LO above the IF and RF frequencies minimizes the relative LO range. In this case, the change in LO frequency is only 1.07:1. Finally, the number of possible harmonic mixing combinations is reduced.

Harmonic mixing occurs when harmonics (or the fundamental) of the LO mix with the harmonics or fundamental of some unwanted signal that is being passed by the input filter. For example, if the desired signal were at 302.5kHz, the LO frequency would be 757.5kHz, and the mixer would be converting the 302.5kHz signal to 455kHz (757.5kHz-302.5kHz=455kHz). However, if the radio is receiving a strong signal at 303.125kHz the fourth harmonic of that signal could be generated in the mixer, mix with the LO fundamental, and be received as a valid signal

4\*303.125kHz-757.5kHz=455kHz.

|              | LO Harmonics |           |         |           |           |  |

|--------------|--------------|-----------|---------|-----------|-----------|--|

| -            |              | 0         | 1       | 2         | 3         |  |

|              | 0            | 0         | 725-785 | 1450-1570 | 2175-2355 |  |

| DE Hammaniag | 1            | 250-350   | 375-585 | 1100-1320 | 1825-2105 |  |

| RF Harmonics | 2            | 500-700   | 25-285  | 750-1070  | 1475-1855 |  |

|              | 3            | 750-1050  | 0-325   | 400-820   | 1125-1605 |  |

|              | 4            | 1000-1400 | 215-675 | 50-570    | 775-1355  |  |

Table 1: Table of possible harmonic-mixing combinations. Each entry shows the range of possible mixer outputs for LO and RF ranges. Any range that spans 455kHz (boldface) can be a source of harmonic mixing.

Table 1 shows the harmonic mixing combinations possible with the mixing scheme used. It can be seen from Table 1 that the lowest-order combination possible is the fundamental of the LO mixing with the fourth harmonic of the incoming RF signal. With the mixer I am using (indeed with most mixers) the most severe harmonic mixing problems involve the fundamental of the signal and harmonics of the LO. Because the LO frequency is above both the IF and RF range, it is impossible to get such a combination with this radio.

There is a second mixing operation in this radio. After the IF is filtered and amplified, it is converted down to audio for demodulation. The IF filter passes frequencies of approximately 500Hz from the IF center frequency of 455kHz. The lowest possible audio frequency that will have the same passband as the IF is 1kHz. Therefore the IF is mixed down to 1kHz with a 454kHz beat frequency oscillator.

The individual blocks in Figure 2.1 are now described in greater detail.

#### 2.2 The Local Oscillator

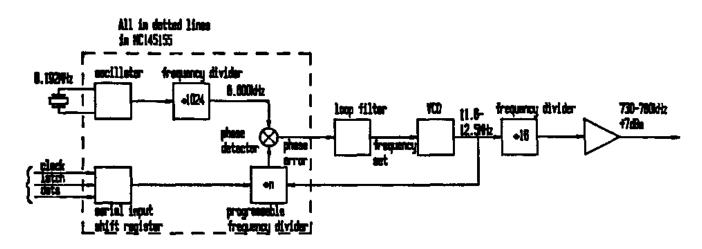

Figure 2 shows a block diagram of the synthesized local oscillator (LO). In the interests of rapid synthesizer lock and low phase noise, I decided to run the VCO at a high frequency and divide it down to the desired LO frequency.

The LO must produce frequencies in the range of 730-780kHz is 500Hz steps, with phase modulation 60dB down from the carrier. If these frequencies were to be synthesized directly, I would need a loop bandwidth of about one radian per second. A loop with such a low bandwidth would have a settling time of about five seconds. Also, because this low bandwidth is achieved by high attenuation in the loop filter, there would be serious stability problems in the oscillator caused by signals bypassing the loop filter and modulating the oscillator directly [8]. If a VCO range of 11.688-12.488MHz in 8kHz steps is used, and the VCO output is divided by 16, the phase modulation criteria can be relaxed by 24dB. This relaxed phase modulation requirement, combined with the higher reference frequency, means that a loop bandwidth of 45 radians per second can be used, for a settling time of about a tenth of a second, and much better oscillator stability.

The core of this synthesizer is a Motorola MC145155 serially programmed PLL frequency synthesis chip [7]. This chip provides a reference oscillator, a pin-programmable frequency divider for the reference oscillator, a serially programmable frequency divider for the output frequency and a phase detector, all on one chip. For this radio, the reference oscillator frequency is 8192kHz, which is divided down by 1024 for a reference frequency of 8.000kHz. The VCO frequency is divided by 1460-1560 then compared to the reference frequency. This results in the VCO output frequency being 11.68-12.48MHz in 8kHz steps.

The output of the VCO is coupled to a 74HC161 divider where it is divided by 16, to a range of 730-780kHz. It is amplified by a 2N3904 transistor stage to the +7dBm needed by the mixer.

The VCO itself is a grounded gate Colpitts oscillator, using an MPF-102 as its active element. The oscillator is tuned by a pair of MV2115 varactors in parallel with a 47pF capacitor and a  $1.4 \,\mu H$  inductor.

#### 2.3 Front end Circuitry

Because the ambient atmospheric noise level is quite high at 300 kHz, I paid much more attention in my design to making a radio resistant to overload, rather than making a radio with an incredibly low noise figure. This goal was achieved by minimizing the pre-mixer gain, and using robust designs for the mixer and post-mixer IF preamp.

#### 2.3.1 Antenna Coupler

A resonant antenna for this frequency band would be on the order of one quarter of a kilometer long. Such an antenna would be inconvenient, even on a large ship. Standard practice for radios of this type is to use a one meter whip antenna and an active antenna coupler and amplifier that provides an impedance transformation between the whip and the 50 input to the RF filter.

#### 2.3.2 RF filter, Mixer

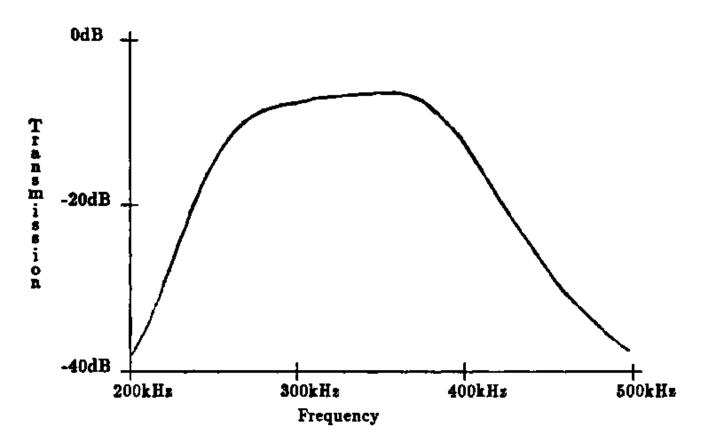

The RF filter is a fifth order Chebychev, with a bandwidth of 50 kHz and center frequency of 300 kHz. It has an overall loss of 7dB. Figure 4 shows the measured shape of the filter passband.

The mixer is a Mini-Circuits GRA-6 diode-ring mixer. It was chosen for its resistance to overload and its ease of use. This mixer requires an LO drive of +7dBm (5mW) and must be terminated with

$50 \Omega$  loads at both the IF and RF ports. If the mixer is driven and terminated properly, it should have a 3rd order intermodulation input intercept of +11dBm<sup>1</sup>.

#### 2.3.3 IF preamp

A preamp is inserted between the mixer and the IF filter. This filter solves a variety of problems that would crop up if a passive impedance matching network were attempted. In order to obtain the best mixer performance, the mixer needs to be terminated by a  $50 \Omega$  load. The IF filter has an input impedance that varies wildly with frequency around the IF center frequency, and it must be terminated at each end with a  $500 \Omega$  resistance in parallel with a 30pF capacitor. Also, the IF filter has about 12dB of attenuation at its center frequency. Furthermore, the match between IF filter and the first IF amplifier was accomplished by a transformer and a ballast resistor, which adds another 2dB of attenuation. Any passive network between the mixer and the IF filter would either have a high amount of loss or would have the same wild impedance variations as the IF filter.

The rated noise figure at the input to the IF amplifier is 6dB [14]. Therefore, the noise figure at the input to the IF filter is about 20dB. In order for the noise figure of the IF preamp to dominate, it had to have a power gain in excess of 20dB. A gain of 24dB was chosen.

The mixer has a 3rd order intermodulation output intercept of +4dBm. Therefore, if the 3rd order intermodulation performance of the radio is to avoid degradation, the IF preamp must have an input intercept that is better than +4dBm. With a gain of 24dB, the output intercept should be +28dBm.

The IF preamp circuit uses heavy feedback both to achieve this intermodulation performance without using too much standing current in the transistor and to provide impedance matching to the mixer and IF filter.

#### 2.4 IF Filter

*Figure 5: Amplitude and phase characteristics of the Rockwell-Collins 526-8627-010 mechanical IF filter*

The IF filter sets the bandpass characteristic of the entire radio. Figure 5 shows the passband characteristics of the IF filter. The filter is a four-pole mechanical filter, Rockwell-Collins part number 526-8627-010. It was made specifically for the conditions encountered in radiobeacon DGPS reception. In particular, it was designed to pass a 400 baud MSK signal with minimal intersymbol interference, while blocking the carrier and ID signal expected to be 500Hz above and below the center frequency of the data stream<sup>2</sup>. It has a 6dB bandwidth of 500Hz, a 100us phase delay bandwidth of 500Hz, and a 60dB bandwidth of 2kHz. At 500Hz away from the center frequency (where one expects to find the radiobeacon carrier or ID signal) it has an attenuation of 25dB. All of the specifications of the filter could be improved with a six or eight pole filter but this filter is adequate for the task.

#### 2.5 IF Amplifier

The radio section was designed for just enough amplification to bring a 5uVrms signal at the antenna up to 1Vrms at the output of the audio amplifier. Because of the other amplifiers in the chain, this works out to an IF amplification of 76dB. I also wanted about 90dB of automatic gain control (AGC) range, to give me AGC action beyond the dynamic range of the front end.

The IF amplifier is a pair of Motorola MC1350 IF amplifier ICs. These provide up to 50dB of gain and 56dB of AGC range each. To get maximum gain, I would have had to use transformer or inductive coupling. Since I did not need this much gain, the amplifiers are resistively coupled. In the end, the IF amplifier chain has about 88dB of gain and over 100dB of AGC action.

## 2.6 2nd Mixer and 2nd Local Oscillator

A demodulator which works at audio frequencies is easier to build than one which works at a 455kHz center frequency. Therefore, the 455kHz IF signal is mixed down to a 1kHz center frequency audio signal.

The mixer used is a Signetics NE602 monolithic mixer chip. This chip has input and output impedances of  $50 \Omega$  and  $1500 \Omega$ , exhibits 18dB of mixer gain, and will provide a 100mV undistorted output. The oscillator in the NE602 is not used. Rather, a CD4060 oscillator/divider and a 7.264MHz crystal are set up to provide a stable 454kHz signal. The output of the CD4060 is attenuated to provide the 200mV p-p signal required by the NE602.

With high IF inputs the NE602 blocks, to the extent that for a large input it can have almost no output at all. This can allow the AGC loop to enter a positive feedback state where increasing IP gain makes the NE602 block and reduce its output, causing the AGC circuit to increase the IF gain, etc. To work around this problem, a pair of diodes were put in parallel across the IF inputs to the mixer, which limits the input amplitude to .6Vp-p. With the input to the mixer limited in this manner, it always has a high enough output to actuate the AGC circuit.

# 2.7 Audio Amplifier and AGC Amplifier

The audio amplifier is a straightforward differential amplifier that provides a voltage gain of 20dB. 10nF capacitors are used to filter out the high frequency components of the mixer output.

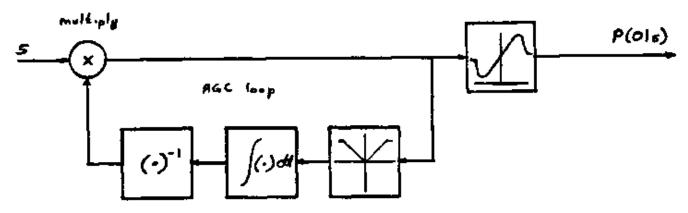

The AGC is designed to keep the signal to the demodulator fairly constant while being insensitive to the large amplitude small duration excursions in the signal envelope that result from lightning noise. The audio peaks are rectified, and the resulting DC is integrated to derive the AGC. The AGC is designed for a time constant of about 200ms.

# 2.8 Microprocessor

The radio is entirely microprocessor controlled. This makes it easy to interface a panel control, digital display, and frequency synthesized LO. Microprocessor control also allows for easy modification to the operation of the radio.

## 2.8.1 The MC68HC11

The Motorola MC68HC11 microcontroller was chosen as the radio CPU for a variety of reasons. It has all the features one would expect in a microcontroller, including the ability to use onboard program ROM, onboard RAM, and comprehensive I/O capabilities. More importantly, it has hardware multiply, various timers that can be configured as timed interrupts or as individual vectored hardware interrupts, and an on board sample and hold A/D converter with four or eight inputs.

As we shall see in later chapters, this processor is fine for my original concept, but it is barely fast enough to run an all software demodulator.

# 3 The Demodulators

Two different demodulators were built for this radio. One uses the microcontroller to sample the MSK at audio, and has the entire demodulator implemented in software. It was designed for very high frequency stability. Its design will be discussed in this chapter. The other is a purely analog design. It runs at a center frequency of 1kHz, and uses CD4046 phase lock loop ICs as its basic frequency reference element. It works well for low to medium noise levels, but cannot maintain lock for high noise levels. Because the analog design does perform well at bit error rates below 10<sup>-3</sup> it is sufficient for non FEC use, so its design is presented in Appendix A.

This chapter is organized as follows. Section 3.1 is an overview of MSK. Once MSK has been explained, a theoretical model for a MSK demodulator is presented. Thus, section 3.2 covers the theoretical model for a MSK detector, assuming that the proper synchronization signals are available, and Section 3.3 covers the theoretical model for the synchronization signal recovery. After the theoretical model is presented (and the reader has an idea of how a MSK demodulator is supposed to work), a microprocessor based demodulator design is presented. Section 3.4 presents the operations performed by the microprocessor based synchronization recovery algorithm and goes in depth into the design of the phase-locked loops in the synchronization recovery algorithm. Finally, section 3.5 presents the operations performed by the microprocessor based detector algorithm.

## 1.7 MSK

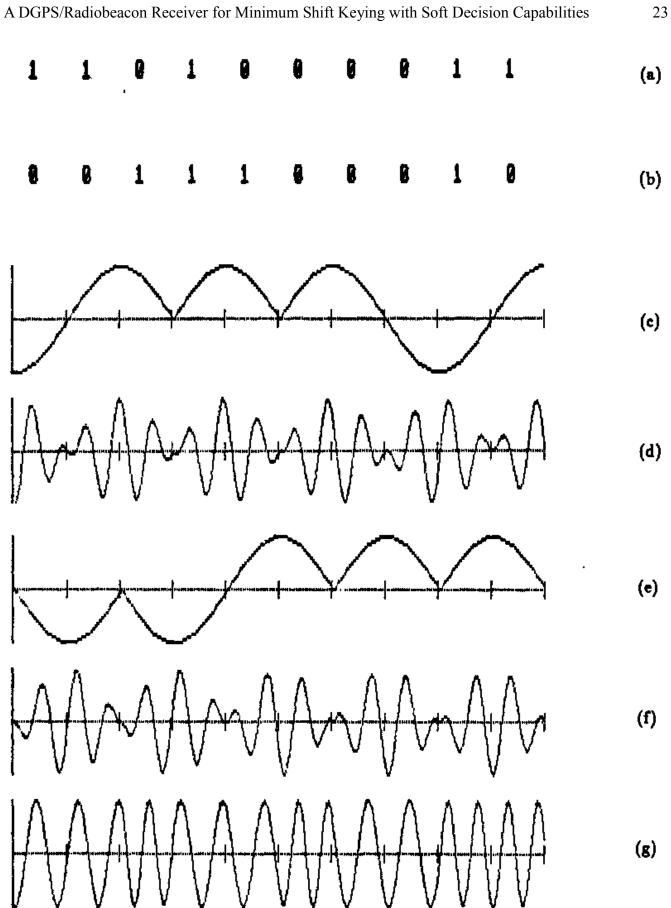

Figure 6: Various waveforms that are part of MSK demodulation

This radio is designed to receive MSK signals. In designing an optimum demodulator for MSK it is best to think of MSK as offset quadrature PSK (OQPSK) with sinusoidal pulse weighting [2]. If

$a_i(t)$  and  $a_q(t)$  are the bits transmitted by the inphase and quadrature components of the OQPSK signal, then an MSK signal would be equal to

$$a(t) = a_t(t)\cos(\pi t/2T_b)\cos(2\pi f t) + a_q(t)\sin(\pi t/2T_b)\sin(2\pi f t)$$

(1)

where  $T_b$  is one bit interval. Figure 11 shows the  $a_i(t)$ ,  $a_q(t)$  and the various components of the MSK signal defined by (3.1). Figure 11(a) shows an example bit stream to be sent.

Like all types of phase modulation, MSK suffers from phase ambiguity at the demodulator. The cure for this is to use differentially encode the bitstream to be sent. Figure 11(b) shows the bitstream of Figure 11(a) after it has been differentially encoded.

This encoded bitstream must be broken up into two parts before being sent over the inphase and quadrature channels. Figure 11(c) shows the inphase multiplier waveform, with the corresponding multiplier values shown as  $\pm 1$  inside the waveform. This encoded waveform is shown multiplied by the inphase carrier to yield the inphase signal in Figure 11(d) [Figure 11(d) is the first term in (3.1)]. Similarly, the sinusoidally shaped quadrature multiplier and the quadrature signal are shown in Figure 11(e) and Figure 11(f). The composite signal, as given by (3.1) is shown in Figure 11(g).

Using a trigonometric identity, (3.1) can be rewritten as

$$a(t) = \cos[2\pi f t + b_k(t)\pi t/2T_b + \phi_k]$$

(2)

where  $b_k(t) = -a_t(t)a_q(t)$  and  $\phi_k(t) = (a_t(t)+1)\pi/2$ . Figure 11 and equation (3.2) show that MSK is an FSK signal with signaling frequencies  $f_m = f + 1/4T_b$  and  $f_a = f - 1/4T_b$ . In addition, a one in our original bitstream corresponds to a high frequency (mark) tone, and a zero in the original bitstream corresponds to a low frequency (space) tone. Indeed (as shall be described later) if one has an easy method to produce phase-coherent FSK with the proper deviation ratio, it is simple indeed to produce MSK.

#### 3.1.1 MSK Detection

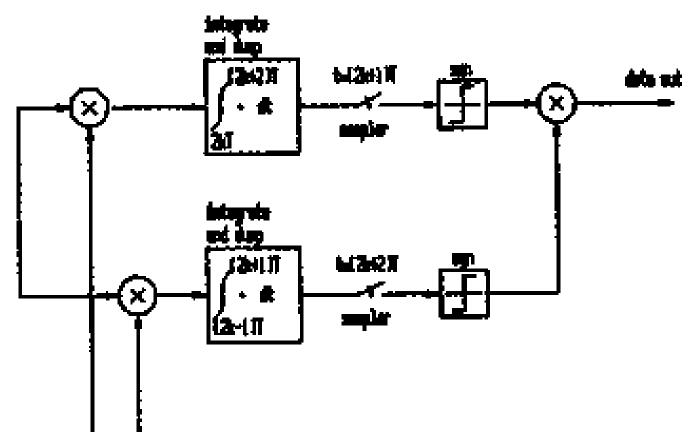

Figure 7: Basic MSK Correlation Detector. This part of the MSK demodulator implements the multiply and integrate-and-dump functions

If one treats MSK as OQPSK it is easy to demodulate. Figure 7 shows a typical MSK demodulator [2]. The incoming signal is multiplied by the inphase and quadrature signals

$z(t) = 2\cos{(\pi t/2T_b)}\cos{2\pi ft}$

and

$y(t)=2\sin(\pi t/2T_b)sin2\pi ft$

(the multiplication by two will become clear later) followed by integrate and dump circuits. This multiply-integrate operation constitutes correlation detection or matched filtering, which is an optimum detection operation for a signal in white Gaussian noise with no intersymbol interference.

Note that this detector is not an optimum detector for non-Gaussian noise. However, interference from the radiobeacon carrier and identification signal (which occurs at approximately  $\pm 500$  Hz) makes wideband signal processing of a 400 baud signal virtually impossible. This detector is near optimum for the signal conditions encountered. If a lower baud rate were to be used with this radio, other, more nearly optimum (wide band) detection schemes for non-Gaussian noise should be investigated (10). These schemes would include hard limiters, clippers, blankers, or some other sort of zero memory non-linearity to suppress the impulse noise.

#### 3.1.2 Synchronization

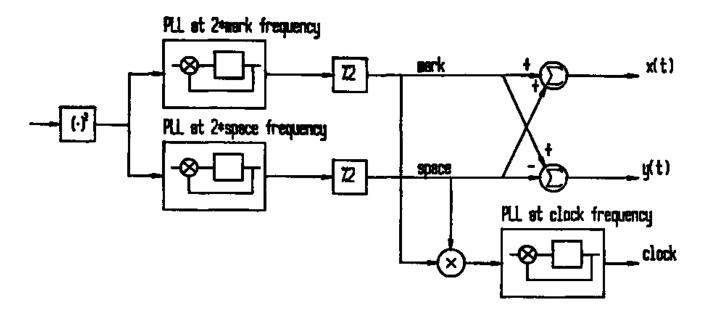

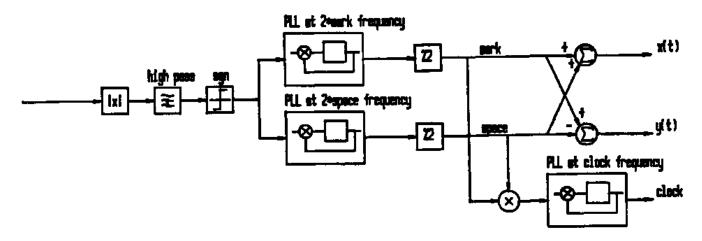

With almost any coherent demodulator, the correlation defector does not require the major effort, rather, the difficulty lies in achieving synchronization with the incoming signal. MSK demodulation is no different. Figure 8 shows an example of a MSK synchronous recovery circuit [2]. If MSK is passed through a squarer, it produces strong discrete spectral components at twice the mark and space frequencies [2]. This becomes apparent if we square (3.2).

$$s^{2}(t) = \cos^{2}[2\pi ft + b_{h}(t)\pi t/2T_{b} + \phi_{k}]$$

=  $(1 + \cos[4\pi ft + b_{k}(t)\pi t/T_{b} + 2\phi_{k}])$  (3)

Notice that the  $2\phi_k$  term becomes either 0 or  $2\pi$ , so it drops out. What we are left with is a pair of tones with a deviation ratio of 1/Tb (known as Sunde's FSK), with the phase for each tone a constant. This means that we can lock onto each of these tones with a phase-locked loop, divide each output frequency by two, and produce the pair of reference signals:

$$s_1(t) = \cos(2\pi f t + \pi t/2T_b)$$

(4)

$$s_2(t) = \cos(2\pi f t - \pi t/2T_b) \tag{5}$$

The sum and difference  $s_1+s_2$   $s_1-s_2$  produce the reference carriers x(t) and y(t) shown in Figure 8. This can be seen by applying trigonometric identities to (3.4) and (3.5):

$$x(t) = 2\cos(\pi t/2T_b)\cos 2\pi ft$$

=  $\cos(2\pi ft + \pi t/2T_b) + \cos(2\pi ft - \pi t/2T_b)$

=  $s_1 + s_2$  (6)

and

Tim Wescott

$$y(t) = 2\sin(\pi t/2T_{b})\sin 2\pi ft$$

=  $\cos(2\pi ft + \pi t/2T_{b}) - \cos(2\pi ft - \pi t/2T_{b})$

=  $s_{1} - s_{2}$  (7)

For a clock reference,  $S_1$  and  $S_2$  can be multiplied:

$$s_{1}(t)s_{2}(t) = \cos(2\pi ft + \pi t/2T_{b})\cos(2\pi ft - \pi t/2T_{b})$$

=  $(\cos 4\pi ft + \cos \pi t/T_{b})/2$  (8)

When this signal is locked onto with a phase-locked loop designed to run at a frequency of  $1/2T_b$ , the output will be proportional to sin  $\pi t/T_b$  which is the desired timing waveform.

#### 3.2 Microprocessor based demodulator

The discrete-time microprocessor based demodulator offers numerous advantages over the continuoustime demodulator. Many of the shortcomings of the continuous-time demodulator could be overcome by careful design and more expensive components, but using a microprocessor based demodulator cures these shortcomings while adding tremendous versatility.

This demodulator is a fairly faithful rendering of the functions delivered by the basic demodulator given in [2] and described at the beginning of this chapter. The block diagrams that describe this demodulator are largely rearrangements of the block diagrams at the start of this chapter (Figure 7 and Figure 8 — basic carrier recovery and basic coherent detector).

A complete listing of the receiver software, including the demodulator routine, is contained in Appendix B.

Frequency stability was the original motivation for going to a microprocessor based demodulator. The low frequency stability available from the CD4046 phase-locked loop chips required such high loop bandwidths that the loops could not maintain lock in the presence of high levels of noise. A crystal based frequency generation scheme would provide the necessary frequency stability. Since a microprocessor based approach offers versatility as well as frequency stability, that approach was chosen. The microprocessor samples data at intervals which are determined by the on board timer. The timer interval is derived from the crystal controlled microprocessor clock, which gives us the required crystal frequency stability.

The demodulator algorithm is implemented as an interrupt routine in the MC68HC11 microcontroller. The routine is called 15 times per bit interval (once every  $166.5 \mu s$ , about six times the audio center frequency) under the control of an output timer on board the microcontroller. It reads the last A/D conversion value, then starts a new conversion.

#### 3.3 The Timing Recovery Algorithm

Since the main motivation for this demodulator was phase stability, I will start my description of the demodulator by describing the phase and bit timing recovery phase-locked loops.

27

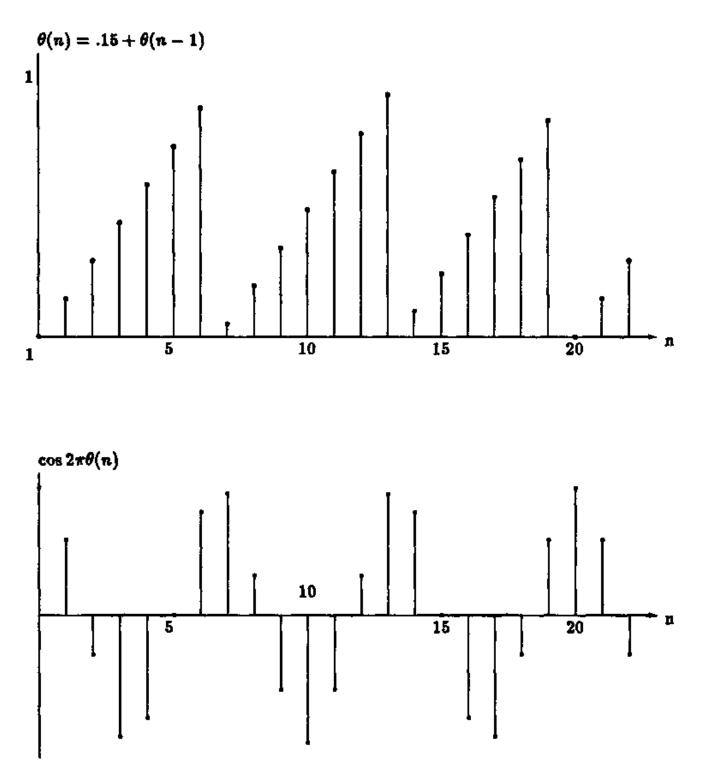

Rather than using oscillators to generate my reference signals, a direct digital synthesis – variable phase ramp approach is used. Figure 9 gives an example of direct digital synthesis. In this type of frequency synthesis, one establishes a phase accumulator with a range of 0 - 1. When the accumulator overflows,

Tim Wescott

www.wescottdesign.com

the phase value just wraps around. If one wants a sinusoidal waveform from the synthesizer, one takes the phase ramp from the accumulator and calculates the sine of the phase.

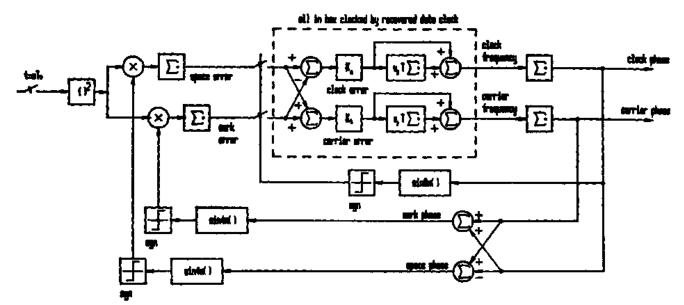

Figure 10: WPI DGPS/Radiobeacon microprocessor based synchronization recovery. This is a block diagram of the operations performed by the synchronization algorithm\* Note that the signal is sampled at approximately 6k he, but that the phase lock loop calculations are performed at the baud rate. This was done to save processing time

Figure 10 is a block diagram of the microprocessor based synchronization recovery algorithm. Notice that this algorithm does not lock to the mark and space frequencies directly. Rather, it translates the mark and space phase errors into clock and carrier phase errors, then locks the clock and carrier to the incoming signal. This was done for two reasons: One, the algorithm is timed by the transitions of the bit clock, so we want to have the bit clock available directly. Two, this allows the option of having different bandwidths for the clock and carrier, which is nice because the clock can be depended on to be much more stable than the carrier.

Because I am using a relatively slow processor, I had to pay quite a bit of attention to writing timeefficient code. Most of the effort involved reducing the amount of processing done during each sample interval. The overall algorithm is separated into two parts. One part is executed every sample interval, and does the minimum amount of processing necessary for one sample interval. This part checks the clock phase before returning. When the clock phase indicates that the end of a bit interval has been reached, the second part of the algorithm is executed. I will indicate in my descriptions of the algorithms which parts are running at the sample speed and which parts are running at the bit clock speed.

I will describe the phase recovery algorithm starting at the output of the phase-lock loop filters, then trace the signal around and finally describe the phase-lock loop filters. I will be using the notation developed in [8] to describe the various parts of the loop.

#### 3.3.1 Phase error estimation

At each sample interval, the clock summer adds the clock increment (proportional to the clock frequency) to the clock phase. Since the clock frequency is approximately 100Hz (one quarter of the bit rate), and the sample interval is  $166.5 \mu s$ , this increment is

$$f_{cl} = T_s(100 \text{Hz}) = (166.5 \,\mu s)(100 \text{Hz}) = .01665$$

where  $T_s = 166.5 \,\mu s$  is the sample interval. The carrier summer works the same, except the increment

$$f_{ca} = 1000 \text{Hz}(166.5 \,\mu s) = .1165$$

The clock and carrier phase become:

$$\theta_{cl}(m) = \left[\theta_{cl}(m-1) + f_{cl}(m)\right] \mod 1 \tag{9}$$

$$\theta_{ca}(m) = \left[\theta_{ca}(m-1) + f_{ca}(m)\right] \mod 1 \tag{10}$$

The mark and space frequencies are symmetrical about the carrier frequency and differ by one half the baud rate. Since the clock frequency is one quarter the bit rate, the mark and space phase can be derived from the clock and earner phase:

$$\theta_m(m) = [\theta_{ca}(m) + \theta_{cl}(m)] \mod 1 \tag{11}$$

$$\theta_s(m) = [\theta_{ca}(m) - \theta_{cl}(m)] \mod 1$$

(12)

The incoming signal is sampled at approximately 6kHz. For timing recovery, this signal is then squared. The mark error is calculated by multiplying the squared signal by a square wave at twice the mark frequency and the result added to a variable for the mark error. The space error is calculated the same way using a square wave at twice the space frequency. Overall, the summer between the phase detector and the loop filters has an effect on noise and stability similar to that of a low pass filter in a continuous-time phase locked loop. As long as the bandwidth of the phase recovery loops are kept fairly low (which is what we want to do anyway) the effect of this summation step on loop stability can be neglected.

In order to execute this multiply and add operation in the minimum of processor time the processor checks the phase, and if it is in the interval [1/4, 1/2) or the interval [3/4, 1) (ie. if the second most significant bit is one) the signal is subtracted from the error variable, otherwise the signal is added to the error variable. This has the effect of a square wave multiply and add, but is much faster for this processor than using the multiply instruction. Ideally, the processor would look up the sine of that phase and do a full multiply and add, but this processor is not fast enough.

#### 3.3.2 The gain blocks

At the end of a bit interval, when the algorithm has collected phase error information, the algorithm goes into the phase-locked loop filter calculations. The clock phase error is calculated from the difference of the mark and space phase errors (the carrier error is calculated from the sum). Because the clock and carrier loops are identical except for the center frequencies and loop bandwidths, I will only describe the clock loop filters. However, I will note any differences between the clock and carrier loops.

If we look at the squarer-multiplier-summer combination as a phase detector, we can calculate the phase detector gain. The peak-peak voltage of the signal present at the input of the A/D converter is 1Vp-p, and its DC average is 2.5V. Eq. (3.2) can be modified to show the signal received at the A/D converter;

$$r(t) = (.5V) \cos[2\pi ft + b_h(t)\pi t/2T_b + \phi_h] + 2.5V,$$

= (.5V) \cos\theta\_r(t) + 2.5V (13)

where  $\theta_r(t) = 2\pi ft + b_k(t)\pi t/2T_b + \phi_k$ . In discrete time,  $r_d(m) = (.5V)\cos\theta_r(mT_s)$  where the variable m represents one sample interval.

This  $r_d$  gets sampled and converted by the microprocessor, and turned into a 2's complement fraction;

$$r(m) = (.1)\cos\theta_r(mT_s) \tag{14}$$

This input signal gets squared, to yield the synchronization signal

$$r^{2}(m) = (.01)\cos^{2}\theta_{r}(mT_{s})i$$

= (.01)(1+cos[4\pi fmT\_{s} + b\_{h}(t)\pi mT\_{s}/t\_{b} + 2\phi\_{h}]) (15)

The mark and space references can be obtained by locking onto this signal with a pair of phase-locked loops at twice the mark and space frequencies, as is done in the theoretical model. Alternately, the loops can be made to lock onto the clock and carrier phases and the mark and space phases can be calculated from them. This algorithm follows the latter approach.

If we have estimates of the mark and space phase errors we can compute the clock and carrier errors. We define the mark and space errors at the start of a bit interval as  $\theta_{sm}(n)$  and  $\theta_{es}(n)$ , respectively (note the use of *n* as opposed to *m* to denote that the interval is a bit interval rather than a sample interval). The clock phase is one half the difference between the mark and space phases, while the carrier phase is one half the sum of the mark and space phases. In other words,

$$\theta_{ecl}(n) = [\theta_{em}(n) - \theta_{es}(n)]/2$$

(16)

(clock phase error)

$$\theta_{eca}(n) = [\theta_{em}(n) - \theta_{es}(n)]/2$$

(17)

(carrier phase error).

The synchronization signal in (3.15) can be used to get estimates of the mark and space phase errors at every bit interval. In the case of the mark phase, the synchronization signal is multiplied by the sine of twice the mark phase:

$$E_m(m) = r^2(m)\sin 4\pi \beta_m(m)$$

= (.005)[1+os2 \beta\_r(m)]sin4 \pi \beta\_m(m)

= (.005)[sin4 \pi \beta\_m(m)+cos2 \beta\_r(m)sin4 \pi \beta\_m(m)] (18)

Tim Wescott

www.wescottdesign.com

This signal has components at either the clock frequency or approximately DC, twice the mark frequency, and at approximately four times the mark frequency. Because the phase locked loops are essentially low pass filters, and because the loop filters are preceded by the summation operation, we can ignore all but the DC component. If a mark is transmitted, we can assume that  $\rho(m) = 2\pi \rho_{c}(m)$

$\theta_r(m) - 2\pi \, \theta_m(m)$  remains constant over the bit interval such that

$$\theta_r(m) - 2\pi \,\theta_m(m) = \theta_{em}(n)$$

and there will be a DC component to  $\hat{e_m}(m)$  :

$$e_m(m) = (.0025)sin2[\theta_{em}(n)]$$

. If a space is transmitted, there will be no DC component, and we can say that

$$\boldsymbol{e}_m(\boldsymbol{m}) = \boldsymbol{0}$$

The error signal  $\hat{e_m}(m)$  is summed over one bit period (15 samples). After this summation, we can assume that all of the AC components of  $\hat{e_m}(m)$  have been filtered out, leaving only

$$e_{dm}(n) = \sum_{m=15n}^{15(n+1)} e_m(m)$$

(because of the low-pass nature of phase-lock loops, any AC that gets passed at this stage will be filtered out later). Note that at the end of a bit period,  $e_{dm}(n)$  has one of two different expected values depending on the bit that was transmitted. If we assume that there is equal probability of a mark or a space being sent, the overall expected value is

$$E \{e_{dm}(n)\} = (.5)E \{e_{dm}(n) | mark transmitted\} + (.5)E \{e_{dm}(n) | space transmitted\}$$

= (.5)(15)(.0025) sin 2[ $\theta_{em}(n)$ ] + 0

= (.01875)(sin 2[ $\theta_{em}(n)$ ])

The forgoing analysis would be identical for the space error, so I won't repeat it here, other than to note that I will use  $e_{ds}(n)$  for my space error variable.

In this algorithm, these mark and space error variables are used to obtain clock and carrier error variables. These are calculated as

$$\boldsymbol{e}_{cl}(\boldsymbol{n}) = \boldsymbol{e}_{dm}(\boldsymbol{n}) - \boldsymbol{e}_{ds}(\boldsymbol{n})$$

for the clock error, and

$$\boldsymbol{e}_{ca}(n) = \boldsymbol{e}_{dm}(n) + \boldsymbol{e}_{ds}(n)$$

for the carrier error.

If we make the approximation that the sine of a small angle is equal to that angle in radians, then we can find the expected value of the dock error estimate for small mark and space phase errors.

$$E \{ e_{el}(n) \} = E \{ e_{dm}(n) - e_{ds}(n) \}$$

= (.1875)( $\theta_{em}(n) - \theta_{es}(n)$ )

= (.0375) $\theta_{ecl}(n)$

Tim Wescott

Therefore, the phase detector gain is

$$K_{d} = \frac{E\left\{e_{cl}(n)\right\}}{\theta_{ecl}(n)} = .0375 \, rad^{-1}$$

The foregoing analysis of the clock loop phase detector gain is exactly the same as the analysis of the carrier loop detector gain. Hence, in my analysis of the carrier loop, I will use eq. (3.23) as the expression for phase detector gain.

The gain of the frequency to phase summer is simply the number of samples per bit times the bit rate;

$K_o = (15)(400 \text{Hz}) = 6000 \text{Hz}$

The other two blocks that contribute phase gain around the loop are the  $k_{hl}$  block, which is the block that the designer can adjust to control the loop bandwidth, and the sin  $4\pi$  block. The sin

$4\pi$  block contributes a gain of  $4\pi rad$  /cycle.

#### 3.3.3 Loop Filter Calculations and Bandwidth

In a phase locked loop the bandwidth is equal to the gain around the loop, so the bandwidth for this loop is

$$\begin{split} K_{cl} &= 4 \pi K_d K_{hl} K_o \\ &= (4 \pi \, rad \, / cycle) (.0375 \, rad^{-1}) (6000 \text{Hz}) K_{hl} \\ &= (2827 \, rad \, / sec) K_{hl} \end{split}$$

. If, for example,  $K_{hl} = 2^{-10}$ ,

$$K_{cl} = (2^{-10})(2827 \, rad \, /sec)$$

= 276 rad /sec

For stability the loop filter requires a zero at  $w_2 < K_{cl}/8$ . In this case, we need  $w_2 < .35 \, rad/sec$  [8]. With  $w_2 = .39 \, rad/sec$ ,

$w_2 T_b = .00098 = 2^{-10}$

We can find the RMS phase error for this loop if we know some details about the input noise. For a phase-locked loop with a squarer at the input, the phase error at the output of the loop is related to the loop bandwidth ( $B_L$ ), input filter noise bandwidth ( $B_i$ ), and input signal to noise ratio ( $SNR_i$ ) [8]. If we assume Gaussian noise, this RMS phase error is

$$\theta_c = \sqrt{\left(\frac{B_L}{B_i SNR_i}\right) \left(1 + \frac{1}{2SNR_i}\right)}$$

. If we assume that FEC will allow valid data reception at a BER rate of .01 out of the demodulator, then we must have phase lock loops that can perform at this noise Level. The theoretical signal to noise level that would cause a .01 BER with the IF filter in this radio is 4.6dB, and the IF filter noise bandwidth is 490Hz. Therefore, the RMS phase error at the output of the loop with a bandwidth of

Tim Wescott

2.76rad/sec would be

$$\theta_a = \sqrt{\frac{.44Hz}{(490Hz)(2.9)} \left(1 + \frac{1}{5.8}\right)}$$

which is more than acceptable.

The carrier phase recovery loop is exactly the same as the clock phase recovery loop, with the exception that the center frequency is 1000Hz rather than 100Hz, and the value of the  $K_{el}$  multiplier may be higher, for a higher loop bandwidth. In practice, it seems that values of  $K_{hl}=2^{-10}$  to  $2^{-6}$  and  $K_{ha}=2^{-6}$  work best (see chapter 4 for test results).

#### 3.3.4 Limit Cycles

The output of the phase detector in this algorithm is a 16 bit fractional number (the value ranges from -.5 to .5, with the smallest possible increment =  $2^{-16}$ ). In a digital control system such as this, one must pay attention to the possibility of limit cycles. A limit cycle is a low-level oscillation in a digital control system caused by the finite resolution of the state variables [13, pp345-353]. To avoid limit cycles of magnitude greater than .088 radians (5 degrees), there must be enough bits of precision at the output of the  $K_{hl}$  multiplier so that at least its lowest order bit is affected by a .088rad error at the phase detector. Similarly, there must be enough bits of precision at the output of the state bit is affected by a .088rad error at the phase detector. For a .088rad error the output of the phase detector will be:

$e_{cl} = (.0375 \, rad^{-1})(.088 \, r) = .0033 < 2^{-6}$

For  $K_{ch} = 2^{-10}$ , the output is less that what can be represented in two bytes;

$$(.0033)(2^{-10}) {<} 2^{-14}$$

The next larger convenient site for the output of the  $K_{hl}$  multiplier is three bytes, which is more than enough precision for our limit cycle criterion. The output of the  $w_2T$  summer is around  $2^{-10}$ smaller than the output of the  $K_{hl}$  multiplier, so the  $w_2T$  summer must have one more byte of precision for a total of four bytes.

Overall, the amount of precision provided is enough for keep the limit cycle amplitude below 4 milliradians, which should be below the expected RMS noise at the output of the loops in all but the quietest of conditions.

The instantaneous frequency is determined by the sum of the outputs of the  $K_{cl}$  and  $w_2T$  summers in Figure 10. In practice, this instantaneous frequency is calculated then stored. The word size chosen for this is three bytes, to match the  $K_{cl}$  summer. Using this size, rather than four bytes, ignores the final byte of the  $w_2T$  summer, but I feel it will not introduce any more limit cycle problems.

#### 3.3.5 Lock Acquisition

Phase lock loops have a linear phase detector characteristic is highly non-linear, and the analysis is very involved, so rather than going into it here the reader is referred to [3] and [8]. One result is presented here however. For our carrier loop, if our initial frequency error is  $W_{ea}$  and the input noise is negligible, the lock time will be

$$T_{pa} = \frac{(w_{ea}/K_{ca})^2 - 1}{w_2}$$

From this we see that the lock time is proportional to the square of the frequency error over the loop bandwidth. Therefore if we want fast lockup and small loop bandwidth, it is important to make sure that the initial frequencies of the clock and carrier loops will be close to their final values. Also, it is a good idea to insure that if the radio receives only noise inputs for a prolonged period of time the loop frequencies do not wander too far away from the correct values.

Three things have been done to deal with these frequency uncertainty problems. One, when the radio is turned on, the microprocessor initializes the loop frequencies to their nominal values (100Hz for the clock loop, 1000Hz for the carrier loop). Two, after every iteration of the  $w_2T$  summers (one for the carrier, one for the clock) the frequency value is checked against frequency limits ( $1000\pm10$ Hz for the carrier, one for the carrier,  $100\pm.5$  Hz for the clock) and if these limits are exceeded, the frequency is set to just inside the limit. Finally, the bandwidth of the carrier loop is larger than the bandwidth of the clock loop.

#### 3.3.6 Carrier Stability and Carrier I\Loop Bandwidth

I mentioned in th last section that the carrier frequency is much less certain than the clock frequency. In this section I will give a rough analysis of why this is, and I will demonstrate the effects of changing the loop bandwidth on carrier reference stability and loop acquisition time.

I will assume that the DGPS/Radiobeacon clock and carrier frequencies are derived by frequency division (or synthesis) from a single crystal controlled source. Therefore, both the clock and carrier frequencies of the transmitted signal can be depended on the be accurate to at least  $\pm 10$  ppm.

There are some frequency references in the receiver that affect the carrier as well: one, the clock frequency reference at the receiver is synthesized from a single crystal controlled source (the microprocessor crystal), two, the receiver carrier frequency reference is affected by the difference between the LO frequency and the BFO (second LO) frequency, which are crystal controlled by two different crystals. Three, the carrier frequency is also affected by the sampling rate of the microprocessor, which is derived by dividing down the microprocessor clock.

We can assume that the initial frequencies of all of the crystal controlled sources in the receiver are adjusted to  $\pm 1$ ppm to start (this is a calibration which can be carried out by the microprocessor at the time the radio is manufactured). We can also assume that the crystal frequency never varies more than  $\pm 10$ ppm with temperature and that the relative crystal error will approximately track with temperature variations.

Ultimately, the clock frequency only depends on the crystal source at the transmitter and the crystal

source at the receiver. Since both of these sources are accurate to  $\pm 10$  ppm , the worst that we can expect of the clock is that it will be 200Hz $\pm 20$ ppm (remember that the clock loop reference is one half the bit rate). It follows that the maximum clock frequency variation at the demodulator will be:

$$e_{fcl} = (200hz)(1*10^{-3}) + (200Hz)(1*10^{-3})$$

= 42.5rad/sec

. This is small enough to be ignored.

The carrier frequency can vary much more. If we assume that the transmitter is accurate to  $\pm 10$  ppm , and that the LO and BFO frequencies track, the carrier frequency variation at the demodulator will be:

$$e_{fca} = (780 \text{kHz} - 454 \text{kHz})(1 * 10^{-5}) + (350 \text{kHz})(1 * 10^{-5})$$

= 6.76Hz

= 42.5rad/sec

Unlike the possible dock frequency error, this error is quite significant. If we wanted the carrier loop to be able to acquire this frequency instantly, we would need a bandwidth larger than 42.5rad/sec. For a loop bandwidth of exactly 42.5rad/sec and a theoretical BER of .01, the rms phase noise in the loop output is

$$\theta_c = sqrtfrac6.76(490 \text{Hz})(2.9)(1 + frac15.8)$$

= .074 rad

which is rather high. To reduce this phase noise, we must reduce the bandwidth of the loop, thereby increasing the acquisition time.

If we use a  $K_{la}$  of  $2^{-8}$  then the carrier loop bandwidth is  $K_{ca} = 11.0$ rad/sec. Using equation (3.27), this gives us an acquisition time of

$$T_{pa} = \frac{\left(\frac{W_{as}}{K_{ca}}\right)^2 - 1}{w_2}$$

$$= \frac{\left(\frac{42.5 \text{rad/sec}}{11.0 \text{rad/sec}}\right)^2 - 1}{.39 \text{ rad/sec}}$$

$$= 36 \text{sec}$$

if we leave the loop zero at  $w_2 = .39 \, rad/sec$ . As a worst case, this acquisition time is bearable, although it could be better. In practice, at room temperature the demodulator attains lock immediately with  $K_{ca} = 11.0 \, rad/sec$ .

Chapter 4 has some test results for the effect various values of the carrier loop bandwidth have on the error rate performance of the demodulator.

#### 3.4 The Correlation Detector

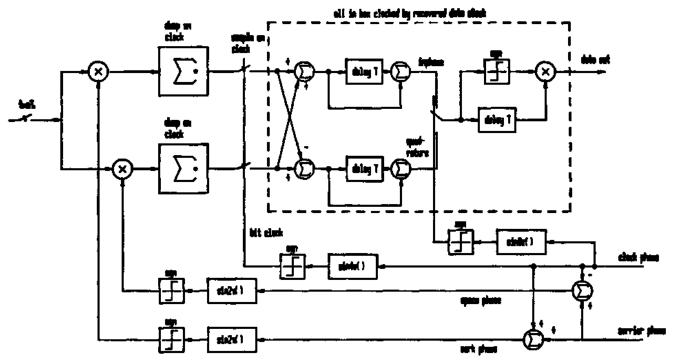

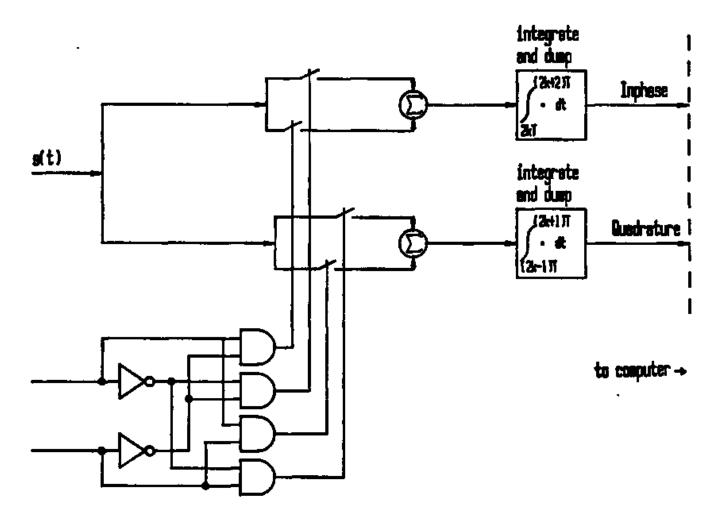

Figure 11: Microprocessor based correlation detector.

Figure 6 shows the block diagram of the correlation detector algorithm used in this radio. With a few exceptions the operations of this detector are exactly equivalent to the operations of the prototypical MSK detector presented at the beginning of this chapter. The two main exceptions are that this demodulator operates in discrete time rather than continuous time, and the multiply operations use square wave inputs rather than sinusoidal inputs in order to speed up the processor.

While the operations performed are the same, the layout is quite different, so I will describe the detector in detail.

The sampled signal, r(m), and the mark and space phases,  $\theta_s(m)$  and  $\theta_m(m)$ , are exactly the same as those used in the synchronization recovery algorithm. Expressions for these variables are given in (3.11), (3.12), and (3.14).

The MSK detector in Figure 7 gets its inphase and quadrature outputs by adding or subtracting the mark and space tones to get the inphase and quadrature signals, then multiplying these signals by the incoming signal. We felt that reducing the inphase and quadrature signals to simple square waves before the multiplication would leave too much information out of the signals. To get around this, the discrete time algorithm multiplies by the constant envelope mark and space tones first, then does the addition/subtraction as a later step.

I will explain the validity of this idea. To make the explanation simpler I will express this with integrations. The concepts are exactly the same for the case using summations. If we let  $d_i(2n+1)$  be the output of the inphase integrator, and  $d_q(2n+2)$  be the output of the quadrature integrator in

Figure 7, these numbers are equal to:

$$\begin{aligned} d_{i}(2n+1) &= \int_{(2n+1)Tb}^{(2n+1)Tb} r(t) z(t) dt = \int_{(2n-1)Tb}^{(2n+1)Tb} r(t) [\cos \theta_{m} t + \cos \theta_{s} t] dt \\ &= \int_{(2n+1)Tb}^{(2n+1)Tb} r(t) \cos \theta_{m} t dt + \int_{(2n-1)Tb}^{(2n-1)Tb} r(t) \cos \theta_{s} t dt \\ d_{q}(2n+1) &= \int_{(2n)Tb}^{(2n+2)Tb} r(t) y(t) dt = \int_{(2n)Tb}^{(2n+2)Tb} r(t) [\cos \theta_{m} t - \cos \theta_{s} t] dt \\ &= \int_{(2n)Tb}^{(2n+2)Tb} r(t) \cos \theta_{m} t dt - \int_{(2n)Tb}^{(2n+2)Tb} r(t) \cos \theta_{s} t dt \end{aligned}$$

. These integrals all integrate over a period of  $2T_b$ , They can be broken up into integrals over  $T_b$ . For example,

$$\int_{(2n)Tb}^{(2n+2)Tb} r(t)\cos\theta_{m}tdt = \int_{(2n)Tb}^{(2n+1)Tb} \int_{(2n+1)Tb}^{(2n+2)Tb} r(t)\cos\theta_{m}tdt + r(t)\cos\theta_{m}tdt$$

I will define a new pair of integrator outputs,  $d_m(n)$  and  $d_s(n)$  to be

$$d_{m}(n) = \int_{nTb}^{(n+1)Tb} r(t) \cos \theta_{m} t dt$$

$$d_{s}(n) = \int_{nTb}^{(n+1)Tb} r(t) \cos \theta_{s} t dt$$

With these definitions, (3.29) becomes

$$d_i(2n+1) = d_m(2n) + d_m(2n+1) + d_s(2n) + d_s(2n+1)$$

and (3.30) becomes

$$d_{q}(2n+1) = d_{m}(2n) + d_{m}(2n+1) - d_{s}(2n) - d_{s}(2n+1)$$

As shown in Figure 6, the demodulator algorithm executes (3.34) and (3.35) in the slower section, while the only operation going on in the faster section is the acquisition of  $d_m(n)$  and  $d_s(n)$  (as given in 3.32 and 3.34). Ultimately, the operations performed by this algorithm ate equivalent to the operations performed in Figure 7 with the blocks rearranged.

This microprocessor-based demodulator ends up working very well indeed. It's performance is less than 1dB worse than the theoretical optimum for this type of demodulator. Test results for this measurement and other pertinent measures of the radio's performance are given in the next chapter.

## 4 Tests of Radio Performance

I tested the radio for its performance under a variety of criteria. These were: demodulation performance in the presence of Gaussian noise, demodulation performance in the presence of nearby CW interference (to simulate the effects of the radiobeacon's own carrier on the radio performance), singlesignal blocking characteristics, two-tone intermodulation input intercept, and receiver equivalent input noise. Each of these tests are discussed in the following sections.

#### 4.1 Bit error rate in the presence of Gaussian noise

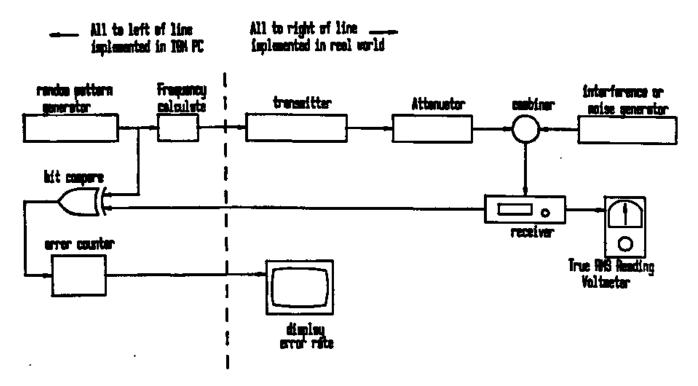

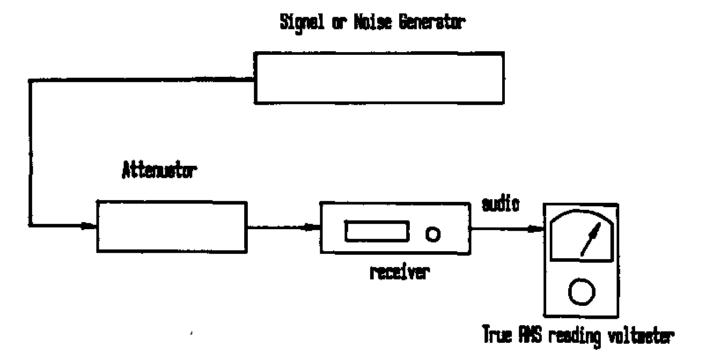

Figure 12 shows the test bed used to obtain measurements of demodulation performance in the presence of Gaussian noise and demodulation performance in the presence of nearby CW interference. Both of these tests are similar in that an interfering signal is added to the intended signal, and the intended signal is adjusted while the bit error rate is measured.

In both cases, the actual bit error rate (BER) is measured with the help of a computer. As shown in Figure 12, the pseudo random sequence is generated by a ten stage tapped shift register, which gives a 1023 bit sequence. The output of this sequence generator is applied to the frequency calculator and the corresponding transmit frequency is sent to the transmitter. The transmitter transmits a mark or a space, then the signal is attenuated and corrupted by either interference or noise. The signal is received by the receiver under test, and the bit decision is compared with an appropriately delayed transmit bit. If the bits do not match, then the error counter is incremented. At intervals, the value in the error counter is updated to the screen.

The following procedure is used to measure the BER vs. signal to (Gaussian) noise ratio (SNR). First, the audio output of the radio is connected to a true RMS reading voltmeter. Then the AGC circuit is defeated, and the radio is connected to a generator of wideband RF Gaussian noise. The IF gain is adjusted until the RMS noise voltage at the the audio output is some convenient value (I used 1V). Next, the noise generator is switched of and the transmitter turned on. The transmitter output is adjusted until the RMS signal voltage is equal to what was established by the noise generator. Finally, the AGC is enabled, and the BER and SNR are measured and recorded for various settings of the transmitter attenuator.

In order to compare the measured performance with the theoretically optimum performance, we must know the relationship that gives  $E_b$  and  $N_o$  given the audio RMS voltage. The filter transmission characteristics (from Figure 2.4) were converted from graphical form to numerical data at 50Hz intervals. This set of data was used to calculate the audio RMS as a function of  $N_o$  and the audio RMS as a function of  $E_b$ . Ultimately, it was found that at a SNR of 0dB the  $E_b/N_o$  ratio is 0.7dB.

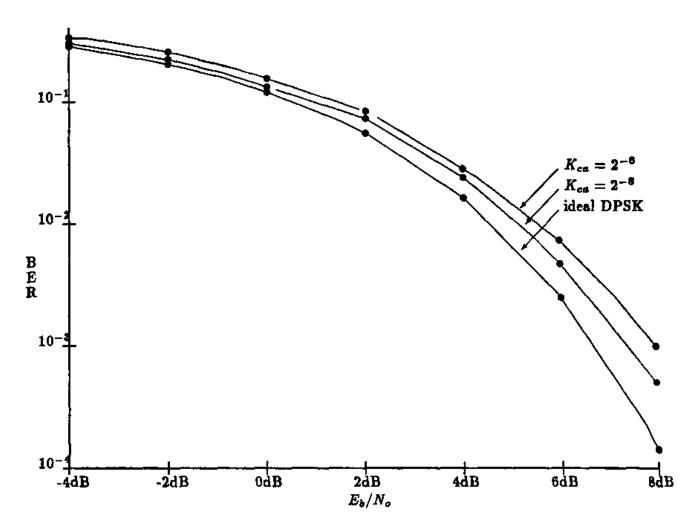

As mentioned in chapter 3, there is a trade off between the carrier loop bandwidth and its acquisition time. To get some data on the effect of carrier loop bandwidths, these tests were conducted for various carrier loop bandwidths. In all cases, the clock loop bandwidth was held constant at 2.76rad/sec.

| SNR  | BER              | BER                                 | BER                                  |

|------|------------------|-------------------------------------|--------------------------------------|

| (dB) | theoretical      | $K_{ca} = 2^{-8}$<br>K = 5.5rad/sec | $K_{ea} = 2^{-6}$<br>K = 22rad / sec |

|      |                  |                                     |                                      |

| 10   | $1.65 * 10^{-6}$ | $2.07 * 10^{-5}$                    | $7.3 * 10^{-5}$                      |

| 8    | $1.41 * 10^{-4}$ | $5.0 * 10^{-4}$                     | $1.00*10^{-3}$                       |

| 6    | $2.5 * 10^{-3}$  | $4.8 * 10^{-3}$                     | $7.4 * 10^{-3}$                      |

| 4    | .0162            | .0239                               | .0285                                |

| 2    | .055             | .072                                | .083                                 |

| 0    | .121             | .133                                | .155                                 |

| -2   | .203             | .222                                | .254                                 |

| -4   | .282             | .30                                 | .33                                  |

| -6   | .35              | .37                                 | .39                                  |

Table 2: Bit error rate vs. SNR for various carrier loop bandwidths

Table 2 lists the performance results for these various loop bandwidths, while Figure 13 presents the results graphically. For the carrier loop bandwidth of 5.5rad/sec, the error rate performance is only .6 to 1dB worse than the theoretical optimum for MSK, which is not too bad.

Notice that the loops managed to maintain lock in the face of noise bad enough to cause a BER of .39. The goal of a demodulator that can perform well in an environment that requires FEC has certainly been demonstrated.

In doing these tests, it was discovered that the loops could not maintain lock for bandwidths greater than  $K = 88 \text{rad}/sec \ (K_{ca} = 2^{-4})$  and would act erratically for bandwidths smaller than

K = 1.4 rad/sec. One can easily predict the loss of lock for the greater bandwidths — all of the stability calculations were done assuming a continuous time loop, and when the bandwidths start to approach the sample frequency the continuous-time approximation falls apart. I believe that the erratic behavior at the lower loop bandwidths is due to phase noise in other oscillators in the system, because the loops were fairly happy with clock bandwidths as low as  $K = .172 \, rad \, sec (K_{cl} = 2^{-13})$ .

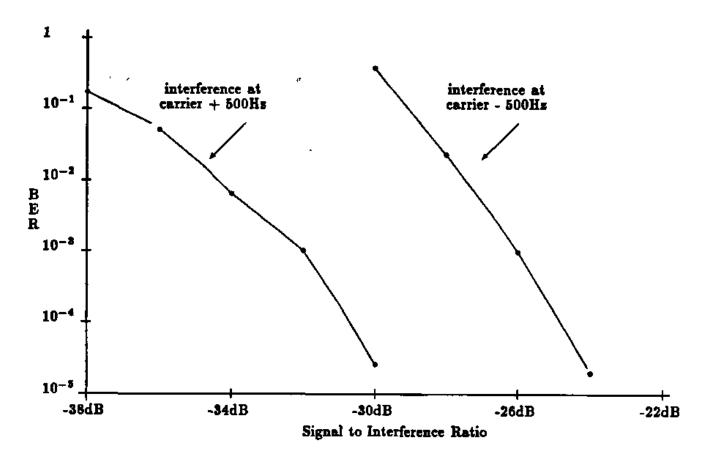

#### 4.2 BER in the presence of an interfering carrier

Measurements of BER in the presence of interfering carriers at 500Hz from the center frequency were done to simulate the effect of the radiobeacon carrier on the demodulator performance, and also to investigate the hypothetical situation of receiving a weak DGPS/Radiobeacon signal in the presence of a strong radiobeacon at a neighboring frequency. I made this measurement at signal levels low enough to avoid any non-linearities in the receiver front end. This test is conducted in exactly the same manner as the Gaussian noise test, with the exception that a CW generator at 500Hz above or below the MSK center frequency is used instead of the RF noise generator.

| SIR  | BER                    | BER                    |

|------|------------------------|------------------------|

| (dB) | $f_r = 288 \text{kHz}$ | $f_r = 288 \text{kHz}$ |

|      | $f_R$ -287.5kHz        | $f_R$ – 288.5 kHz      |

| -22  | 0                      | 0                      |

| -24  | $2.0 * 10^{-5}$        | 0                      |

| -26  | 9.5*10 <sup>-4</sup>   | 0                      |

| -28  | .023                   | 0                      |

| -30  | .37*                   | $2.6 * 10^{-5}$        |

| -32  | *                      | $1.0*10^{-3}$          |

| -34  | *                      | $6.5*10^{-3}$          |

| -36  | *                      | .051                   |

| -38  | *                      | .171                   |

| -40  | *                      | .21*                   |

| -42  | *                      | *                      |

*Table 3: Bit error rate vs. signal to interference ratio. Entries marked with an asterisk (\*) represent interference levels where the loops have lost lock*

Table 3 lists the results of this test for interfering frequencies that are 500Hz above and 500Hz below the desired receive frequency. Figure 14 presents these results graphically. When the data was taken at high error rates the demodulator took a long time to recover from the interference, which suggests that the input interference affects the phase-lock loops. Notice that the error rate goes from very good to horrible in a very small span of input power. This is most likely because the interfering signal overwhelms the squaring function in the phase locked loops at this point. Also notice that the resistance to this interference is 10dB better when the interference is on the low side of the signal. When the interference is 500Hz below the carrier at RF, it hits a frequency of 1500Hz at audio, which places it at the sampling frequency of the demodulator. After sampling, this interference is very close to DC, and should be modulated out of existence in the phase-lock loops.

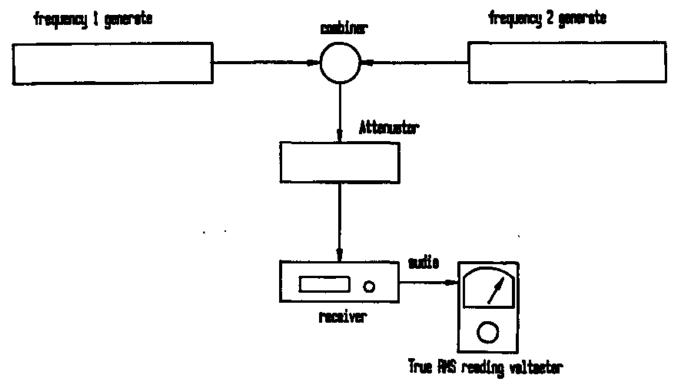

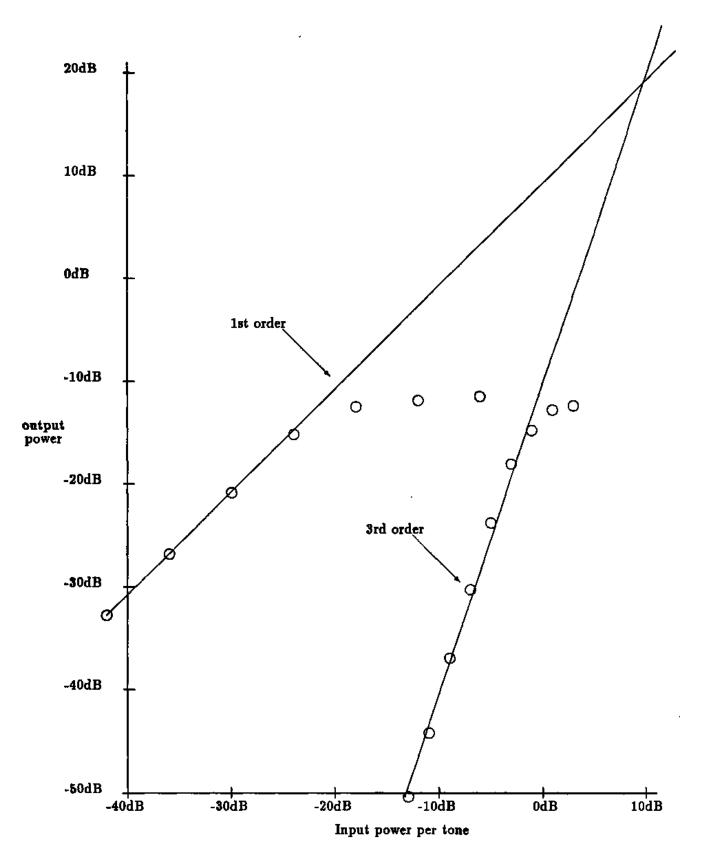

#### 4.3 3rd Order Inter modulation Performance

Figure 15: 3rd order intermodulation test bed

Figure 15 shows the test bed used to obtain a measure of the 3rd order intermodulation performance of the receiver. In order to measure this performance, the receiver gain from the RF input to the audio output (demodulator input) was measured at 287.5kHz RF input for a given IF gain setting (the AGC was once again disabled). Then a pair of signals at 302.5kHz and 317.5kHz was applied to the RF input and the resultant audio output (the 3rd order intermodulation product) was measured as the signal power was varied. Figure 16 shows the numerical results of these tests. When the two sets of input power vs. output level data are plotted as in Figure 16, one can calculate the 3rd order intermodulation intercept. For this radio, this intercept comes out to be +9.8dBm. This is neither very good, nor what was expected. The mixer input intercept is around +11dBm, and the RF filter has about 7dB of loss, so the input intercept to the radio should be around +18dBm. I suspect that the problem is either the termination of the mixer or, more likely, that the IF preamp is not robust enough.

Tim Wescott

#### 4.4 Receiver Noise Floor

The test setup in Figure 17 was used to measure the noise characteristics of the receiver. The receiver AGC was disabled, and a small signal was injected to the receiver at its RF port, and the signal magnitude was adjusted until the output at audio was 10dB greater than the output with no signal input. This occurred at an input carrier amplitude of 104.7dBm. From this we can deduce the effective noise power at the input to the receiver. This is

*noise power* = -104.7dBm-9.5dB = -114.2dBm

. This is also known as the 'noise floor' of the receiver. Knowing the noise floor of the receiver and the effective noise bandwidth of the IF, we can deduce the receiver noise figure:

$NF = 168 \text{dBm} + noise floor - 10 \log(B_i)$ = 168 \text{dBm} - 114.2 \text{dBm} - 10 \text{log}(490) = 27 \text{dB}

Notice that this is not a very good noise figure, but since we are putting the antenna coupler before the RF input to the radio, we can reduce the overall effective input noise by increasing the amplification in the antenna coupler. Overall, the tests of demodulator performance were very encouraging, and the tests of the basic radio performance were rather disappointing. In a way this is not surprising. We ended up expending much more effort on the demodulator design for this radio than we did on the basic radio itself. I think that were one to implement this radio as a practical design, some design effort should be expended to make the radio a little more robust and a little less noisy.

# 5 Summary, Some Comments on Soft Bit Decisions, and Further Work

#### 5.1 Summary

I have described a radio receiver built to receive MSK in the 285-325kHz bands. This receiver does this job well. The most notable features of this receiver are its ability to be modified for soft bit decisions, its ability to maintain demodulator lock for very high noise levels, and the microprocessor based demodulator, which is by its nature very flexible.

#### 5.2 Some Comments on Soft Bit Decisions

The original aim of the work in this thesis was to develop a radio/demodulator combination that could give soft bit decisions (or generate side information - the two are equivalent). While this goal was not achieved, quite a lot of groundwork has been done in the development of hardware and software to get the job done.